페이징(Paging)이란?

논리주소의 메모리를 고정된 크기의 페이지(Page)로 나누어 관리하는 기법이다.

페이징은 아래와 같은 특징들을 갖고 있다.

- 물리주소 공간(Physical address)은 연속적이지 않을 수 있다(noncontiguous)

- 페이지는 모두 같은 크기를 가진다.

- 물리주소 공간을 페이지와 같은 사이즈로 나눈 것들을 프레임(Frame)이라고 한다.

- 페이지 사이즈(=프레임 사이즈)는 하드웨어에 의해 정해진다.

- 페이지의 크기는 일반적으로 2의 제곱수를 사용한다. 일반적으로 4KB(2^12) ~ 1GB(2^20)

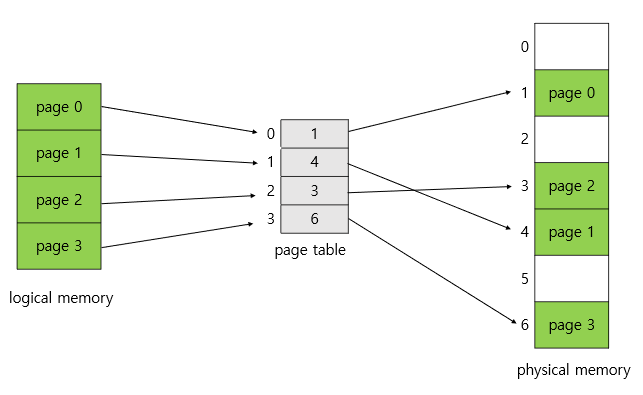

- 페이지 테이블(page table)을 이용해 논리주소에서 프레임을 가리키는 물리주소로 매핑한다.

- 외부 단편화는 발생하지 않으나, 내부 단편화는 발생한다.

페이지 테이블(Page Table) 이란?

페이지 테이블은 논리주소의 페이지를 물리주소의 프레임으로 매핑시켜주는 정보를 담고 있는 테이블이다.

페이지 테이블은 다음과 같은 특징들을 갖고 있다.

- 페이지 테이블은 per-process 데이터 구조이다. 즉, 모든 프로세스가 페이지 테이블을 가지고 있다.

- 페이지 테이블은 메인 메모리에 저장된다.

- Page Table Base Register(PTBR)가 페이지 테이블을 가리키고 있다.

- Page Table Length Register(PTLR)가 페이지 테이블의 사이즈를 가리키고 있다.

- 이러한 레지스터들의 내용은 PCB에 저장되어 있다. 따라서 문맥교환(context switching)이 일어날 때 교체된다.

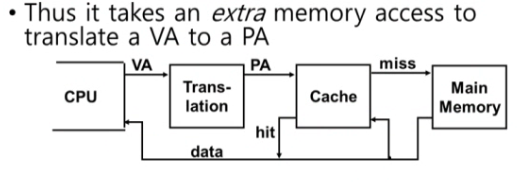

- 모든 data/instruction 접근은 두 번의 메모리 접근이 필요하다 -> 페이지 테이블에 접근하는 overhead가 존재한다.

- 한 번은 페이지 테이블 접근, 한 번은 실제 physical 메모리 접근

- 두번의 메모리를 접근해야 하는 문제는 fast-lookup hardware cache라고 불리는 associative memory 혹은 translation look-aside buffers(TLBs)를 이용해 해결할 수 있다.

요구 페이징, Demand Paging

CPU에 의해 프로세스가 수행되기 위해서 적재할 페이지를 언제 가져올 지에 관한 내용이다.

프로세스가 수행되는 시점에 특정 페이지를 메인 메모리에 적재하는 것이다.

다시 말해서 요구된 페이지만을 메인 메모리에 적재한다.

동시에 모든 페이지를 적재하지 않으며 이런 식으로 수행하는 것은 사용되지 않는 페이지를 기억장치에 읽어들이는 것을 예방하고 교체시간, 메모리 공간를 절약하고 다중 프로그래밍 정도를 높일 수 있다.

요구 페이징은 메인메모리에 실행할 프로세스의 페이지가 전혀 없어도 프로세스는 수행을 시작할 수 있게 하고 프로세스는 최초의 명령부터 page miss를 일으킬 뿐이고 그냥 필요한 page에 적재하면 된다.

다만 page miss가 일어났을 때에는 Disk에서 읽어오므로 오버헤드가 크다. 또한 개별 프로그램의 처음 시작할 때에는 지연이 발생한다. 그리고 페이지 교체 알고리즘의 영향을 많이 받는다.

page table에는 어떻게 접근을 할까?

page table은 Main Memory에 있는데 레지스터로 하면 더 빠를 것 같지만 레지스터 가지기엔 용량이 너무 커서 그렇다.

메인 메모리에 접근하려면 page table을 이용해야하는데 page table이 메인메모리에 있으면 page table의 위치와 page table의 크기는 레지스터가 가지도록 한다. 위에서 PTBR, PTLR이 그 역할을 수행한다.

메모리에 페이지 테이블을 저장하면 문맥 교환 속도가 빨라지지만 메모리 액세스 시간이 느려질 수 있다. 다시 말해서 메모리에 접근하기 위에 page table에 접근하고 다시 메모리에 접근하는 2번의 access가 필요해진다. CPU,OS가 쓰는 가상메모리 주소는 물리적 주소와 다르다. 때문에 가상메모리에서는 물리적 주소로 바꾸는 작업이 필요하다. 이것을 Address Translation이라고 부른다.

CPU에서는 VA를 쓰지만 캐시 메모리, 메인 메모리에선 PA, Physical Address를 쓴다. 때문에 Translation은 CPU와 캐시 사이에서 발생한다.

Translation 작업에는 Main memory 접근을 필요로 한다. ** page table은 Main memory에 존재한다. 즉, 캐시에서 Miss가 난다면 접근을 2번이나 해야하는 비용이 높은 작업을 해야한다는 것이다. 이를 극복하기 위해 TLB라는 장치를 만들었다. Translation Lookaside Buffer로 최근에 Translation 했던 정보를 담는 버퍼다. 해당 버퍼는 캐시역할을 하며 최근에 접근한 page에 대한 물리적 주소를 저장해놓는다. (물론 일부만 저장) 만약 해당 정보에 Translation 정보가 있다면 Main Memory를 access하지 않아도 되어 비용을 줄일 수 있다. 즉, 메인메모리 Pagetable lookup 하는 과정을 줄이는 것이다.

page fault(miss), 페이지 폴트(부재)

해당 페이지에 내가 원하는 data가 없는 것으로 page fault는 Disk에서 page를 불러오는 작업(replace)을 해야만한다.

Disk에서 가져오는 일은 무척 비용이 큰 일이므로 **Page의 miss는 OS가 관리한다.

Page fault 이후에는 page replace가 일어난다. page fault로 일어난 작업이다. 즉, Disk 에서 읽어오는 작업은 비용이 정말 큰 작업이다. 교체가 일어날 땐 보통 최근에 쓰지 않은 순서대로 페이지를 교체해 나간다. (LRU)

'CS > OS & 하드웨어' 카테고리의 다른 글

| 캐시가 동작하는 아주 구체적인 원리 (0) | 2022.12.26 |

|---|---|

| 캐시 히트율/메모리 적중률 (Hit Rate) (0) | 2022.12.26 |

| 바이오스 (BIOS - Basic Input/Output System) (0) | 2022.11.13 |

| 펌웨어 (Firmware) (0) | 2022.11.13 |

| 내부 및 외부 단편화 (Internal/External Fragmentation) (0) | 2022.10.28 |